新闻中心

芯科普 | 一文了解DDR3/DDR4/LPDDR4的接口差异

2023年08月18日

DDR3/DDR4/LPDDR4三者的不同点从外部来看主要是通过不同的接口来实现。因此我们从接口实现上来看这三者之间的差异。

DDR3/DDR4/LPDDR4三者的不同点从外部来看主要是通过不同的接口来实现。因此我们从接口实现上来看这三者之间的差异。

![]()

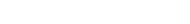

DDR3的接口为SSTL(Stub Series Terminated Logic),匹配电阻上拉到VDDQ/2。

![]()

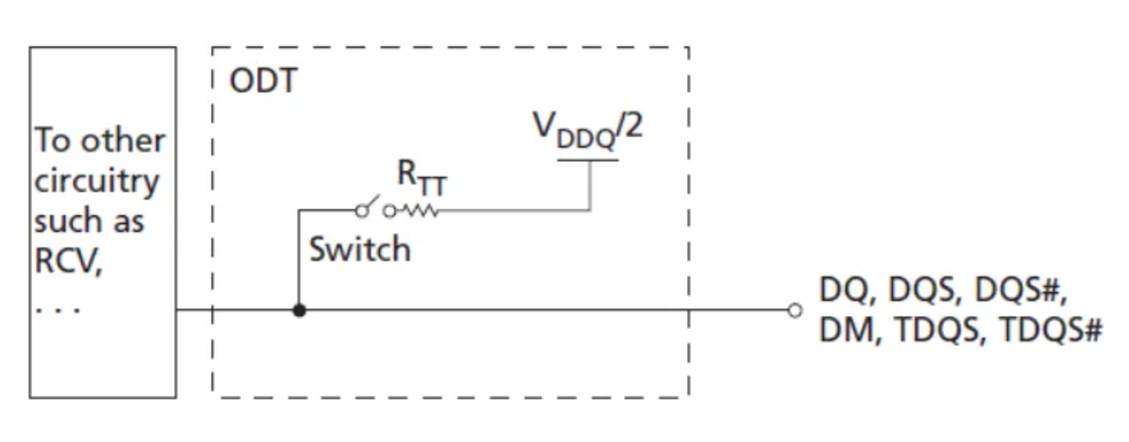

DDR4匹配电阻上拉到VDDQ,可称为POD(Pseudo Open Drain),用以减少IO电流消耗。对DDR4的POD来说,drive High(logic level ”1” )几乎不耗电,可以用这特点搭配DBI(Data bus inversion)来降低功耗。当一个字节里的 ”0” bits比 ”1” bits多时,可以使能DBI,将整个字节的“0”和“1”反转,这样 “1” bits就会比“0” bits多,达到省电的效果。

![]()

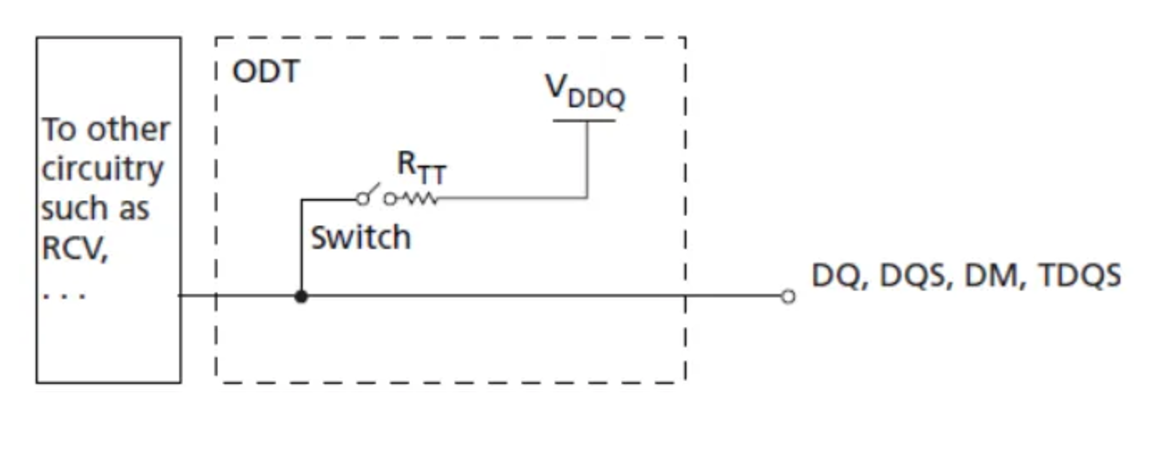

LPDDR4的匹配电阻下拉到VSSQ, 称为LVSTL(Low Voltage Swing Terminated Logic), 这样可以更省电,LPDDR4靠NMOS 晶体管pull up,也可以工作在更低的电压。

从上述DDR3到LPDDR4接口设计的演变的呈现,其目的主要是是为了满足产品对低功耗的要求,因此其工作电压也变得越来越低。

从上述DDR3到LPDDR4接口设计的演变的呈现,其目的主要是是为了满足产品对低功耗的要求,因此其工作电压也变得越来越低。

相关新闻

芯科普 | 一文了解嵌入式存储在WiFi6路由器的应用

只要出去吃饭、逛街,我们都会询问是否有WiFi,密码是多少。Wi-Fi早已成为人们生活和工作中必不可少的最基本的需求之一,WiFi6被认为是与5G平起平坐的创新无线技术。

2024年05月14日

芯科普 | 嵌入式存储芯片Nand Flash的常见封装类型

随着目前电子产品小型化的需求越来越多,且可穿戴设备的逐渐普及,工程师们对于芯片小型化的需求也越来越强烈,这个就涉及到了芯片的封装工艺。

2024年06月28日

芯科普 | 手机主流存储eMMC、UFS与NVMe的区别

近几年,手机影像不断发展,照片+视频占据大量存储空间,在愈发膨胀的微信、手游以及各种APP面前,存储空间愈发不够。该存储空间即是手机存储容量(ROM),市面上常见的手机快闪记忆体标准共有eMMC、UFS与NVMe。

2024年07月05日

芯科普 | 一文了解DIMM

DIMM,全称Dual-inline-Memory-Modules,即双列直插式内存模块,是在奔腾CPU推出后出现的新型内存条,是在单列直插内存模块(single inline memory module,SIMM)的基础上发展起来的,SIMM提供32位数据通道,而DIMM则提供了64位的数据通道。

2024年07月16日